## INTEGRATED CIRCUITS

1988 Apr

## 74FXXXX "Light Load" input products

### AN215

### Major "Light Load" Input Features

- Patented "Light Load" NPN input structure Normal Input pins = ±20μA per input Transceiver I/O pins = ±70μA per I/O pin Primarily capacitive loading = <10pF</li>

- Ideal for MOS CPU, peripherals, and semi-custom bus interfaces

- Patented turn-OFF speed-up circuit

- No significant speed disadvantage standard 74F speeds

- PC board transmission line drive capability: -15/64mA I<sub>OH</sub>/I<sub>OL</sub>

- "Broadside" design in 20-, 24-, and 28-pin slim-DIP packages

- "Light Load" family includes:

- 19 Buffers and line driver parts

- 19 Shift register, register and latch parts

- 19 Transceivers (no storage)

- 8 Dual registered transceivers

- 7 Arithmetic functions

#### Introduction

The Philips Semiconductors 74F "Light Load" product line is a high performance, TTL bus compatible series of very low input bias current ( $\pm 20\mu$ A), buffer/driver, transceiver, register, multiplexer and arithmetic MSI functions. The patented "Light Load",  $\pm 20\mu$ A NPN input structure, shown in Figure 1, combined with a unique input speed-up circuit (also patented) makes this product line ideal for interfacing with all MOS devices, without any speed degradation. When compared to the I<sub>IL</sub> of standard FAST inputs of 600 $\mu$ A (larger for some other logic families) this "Light Load" input shows a 30:1 reduction in I<sub>IL</sub> loading (600 $\mu$ A/20 $\mu$ A).

These devices were specifically designed to meet the requirements of buffering low output drive MOS VLSI/LSI devices from the rigorous loading environment PC board/motherboard buses and system backplanes. The "Light Load" inputs and improved speed performance make this product line ideal for interfacing to low output drive capability, slower MOS CPU, peripherals and semi-custom chips used in most state-of-the-art logic designs today. Using these "Light Load" input bus products, MOS chip outputs will only have to drive the small amount of distributed PC trace capacitance and inductance loading. The MOS device output drive capability is not wasted on drivers/transceivers with large DC input current drive requirements.

See Table 1 for a complete listing of the part numbers and functions of the "Light Load" product line.

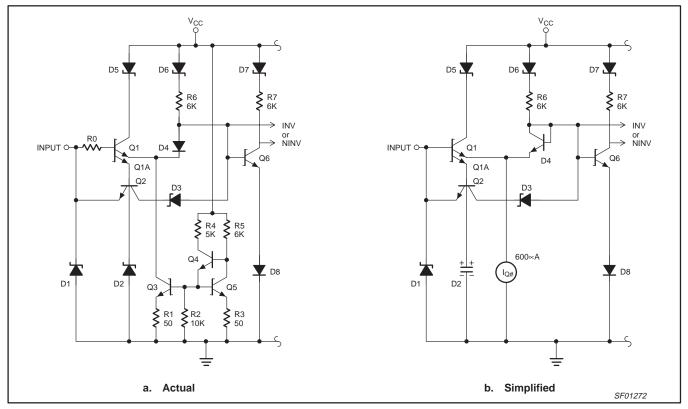

Figure 1. The "Light Load" and Speed-Up Circuit Input Structure (Actual & Simplified)

### 74FXXXX "Light Load" input products

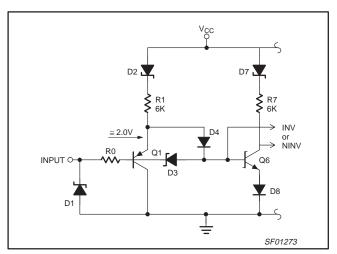

Figure 2. Future "Light Load" PNP Input

### "Flow-Through" Design

Figure 3 illustrates the pin configurations of the 74F84X Latched Buffer series. Notice that all of the "Light Load" input data bus products use a "Flow-Through" design which allows logic signals to flow into one side and out of the other without crossing or folding back on signal paths such as the 74F24X octal series. Comparing the physical PC board signal bus path layout required for the 74F845 Octal Registered Buffer to that of the zig-zag signal path of the 74F240 Octal Inverting Buffer, you will see the significant advantages of this product line's "Flow-Through" design in simplifying the design and layout of large, bus-oriented PC boards.

The "Light Load" input product line combines "Flow-Through" design, high speed performance and high functional density into 20-, 24-, and 28-pin, 300-mil Slip-DIP packages significantly reducing system propagation delays, parts count, power dissipation, PC board area/complexity and, therefore, total cost while enhancing total system reliability.

| F841/2 | F843/4 | F845/6 |    |    | F845/6            | F843/4            | F841/2            |

|--------|--------|--------|----|----|-------------------|-------------------|-------------------|

| OE     | ŌĒ     | OE0    | 1  |    | V <sub>CC</sub>   | V <sub>CC</sub>   | V <sub>CC</sub>   |

| D0     | D0     | OE1    | 2  | 23 | OE2               | 00/00             | 00/00             |

| D1     | D1     | D0     | 3  |    | 00/00             | 01/ <del>01</del> | 01/01             |

| D2     | D2     | D1     | 4  |    | 01/01             | 02/02             | 02/02             |

| D3     | D3     | D2     | 5  |    | 02/02             | O3/ <del>O3</del> | 03/ <del>03</del> |

| D4     | D4     | D3     | 6  |    | 03/ <del>03</del> | 04/04             | O4/ <del>04</del> |

| D5     | D5     | D4     | 7  |    | 04/04             | O5/ <del>O5</del> | O5/O(5            |

| D6     | D6     | D5     | 8  |    | 05/ <del>05</del> | 06/ <del>06</del> | O6/ <del>06</del> |

| D7     | D7     | D6     | 9  |    | 06/ <del>06</del> | 07/07             | 07/07             |

| D8     | D8     | D7     | 10 |    | 07/07             | 08/ <u>08</u>     | 08/ <del>08</del> |

| D9     | MR     | MR     | 11 |    | EN                | EN                | O9/O9             |

| GND    | GND    | GND    | 12 |    | LE                | LE                | LE                |

|        | L.     | ★      |    |    |                   |                   |                   |

|        |        |        |    |    |                   |                   | SF01274           |

Figure 3. 74F84X Latched Buffer Pin Configurations

### 74FXXXX "Light Load" input products

#### Input Structure – Differential Amplifier

Figure 1 shows the circuit diagram of the patented "Light Load" NPN input (Q1/3, R6, & D4) and the Turn-OFF Speed-Up circuit (Q2, D2, & D3). This input structure is actually a linear differential amplifier consisting of Q1, D4 and a constant current sink made up of Q3/4/5 and R1/2/3. The input bias current of this amplifier is less than  $\pm 20\mu$ A for V<sub>1</sub> between 0.0V and 5.5V. The Turn-OFF Speed-Up circuit (D2/Q2/D3) quickly discharges Q6's base-collector stored-charge to ground. the following analysis assumes room temperature and 5.0V<sub>CC</sub> operation.

The Q1's base is the input side of the differential amplifier and D4's anode is the reference side. When the input is HIGH (2.0V), Q1 is turned-ON and I<sub>CE</sub> plus I<sub>BE</sub> current flows into Q3's constant current sink network of ~600 $\mu$ A. Since D4's anode is clamped at 1.3V to 1.4V by the V<sub>BE</sub> of Q6 plus D8's voltage drop, and since Q1's emitter voltage is pulling the cathode of D4 up to greater than ~1.4V (the 2.0V<sub>IH</sub> minus Q1's 0.6V<sub>BE</sub>), R6's (6K) current cannot flow through D4 and forward biases Q6's base-emitter.

Since Q6 is a Schottky clamped transistor, it has a  $V_{CEsat} \sim 0.5V$ . When Q6 is turned-ON by R6, the voltage at its collector drops to ~0.9V from ground (adding in D8 voltage drop), which turns-OFF the output totem-pole pull-down driver transistors and turns-ON the pull-up. This topic will be discussed in more detail in the next section (refer to Figure 4).

#### Input Structure – Constant Current Sink

The constant current sink produced by Q3/4/5 and R1/2/3/4/5 sinks a relatively constant  $600\mu$ A to ground. this "current mirror" circuit drives the base-to-ground voltage of Q3 and Q5 to Q5 V<sub>BE</sub> plus the voltage drop across R3. Since Q3 and Q5 are identical, the voltage drops across R1 will equal that of R3. Therefore, the current through R1 equals the current through R3 times the ratio of R3:R1.

The base bias currents for Q3 and Q5 is supplied by Q4. Because of the relatively high  $\beta$ s of Q3 and Q5 (>50), their base currents of ~10µA do not significantly effect the currents through R3 and R1 ( $\beta$  or BETA = transistor current gain). At 25°C and V<sub>CC</sub> = 5.0V, R3's current is approximately equal to:

$I_{R3} = [V_{CC} - (V_{BE-Q4} + V_{BE-Q5})]/(R3 + R5)$

${\sf I}_{\sf R3} = (5.0 {\sf V} - 1.2 {\sf V}) / (50 \Omega + 6000 \Omega) \cong 600 \mu {\sf A}$

Therefore:

$I_{CE-Q3}\cong I_{R1}=I_{R5}\times (R3/R1)\cong 600\mu A$

With Q1's  $\beta$  also greater than 50, the HIGH logic level input bias current is less than 20µA:

$I_{OH} = I_{CE-Q3}/BETA_{Q1} \cong 600\mu A/>50) < 12\mu A$

#### The "Light Load" PNP Input

We will soon be introducing a new product line of "Light Load" PNP devices. One of the first products will be the 74F821 through 74F826 Registered Buffers, which will have the same pin configurations and options as the 74F841 through 74F846 Latched Buffers (see Figure 3). The 74F82X series will provide a positive-going edge triggered clock input to its 8-, 9-, and 10-bit register storage parts versus the 74F84X series' HIGH level Latch Enabled latches.

With Philips Semiconductors latest oxide-isolated process, a new, high performance "Light Load" PNP input structure will soon be available. This new PNP input, shown in Figure 2, provides a high impedance AND input structure versus the NPN input OR input and reduces the chip power dissipation by eliminating the requirement for a constant current source for each input.

The PNP input is still a differential amplifier with the cathode of D3 referenced to 2 V<sub>BE</sub> voltage drops from ground. When the input is HIGH (V<sub>IH</sub>  $\geq$  2V), no Q1 emitter-base current can flow because the anode of D3 is clamped to the 2 V<sub>BE</sub>. As D4 forward biased with the current from R1, the output driver transistor (Q60 turns ON. When the input is LOW (V<sub>IL</sub>  $\leq$  0.8V), Q1's emitter-base junction is forward biased, which turns ON the  $\beta$  amplified emitter-collector current of Q1. When Q1 is ON, the anode of D4 is clamped OFF by the input V<sub>IL</sub> voltage plus Q1's emitter-base drop (V<sub>IL</sub> + Q1<sub>VBE</sub>  $\leq$  0.8V + 0.6V = 1.4V). Therefore, the input threshold at the base of Q1 is  $\cong$  1.4V (2 V<sub>BE</sub>) at 25°C.

With the  $\beta$  of Q1 typically greater than 100, the  $V_{IL}$  input bias current is guaranteed to be less than 20µA. With the input HIGH, the input leakage is also guaranteed to be less than 20µA. The  $\beta$  amplification of Q1 is basically the only difference between this PNP input's 20µA  $I_{IL}$  and the standard diode input's  $I_{IL}$  of 600µA.

When the base of Q1 is switched LOW, the Schottky diode D3 provides a turn-OFF speed-up path to ground, which quickly discharges the base of the driver transistor (Q6).

### 74FXXXX "Light Load" input products

#### **Output Structures**

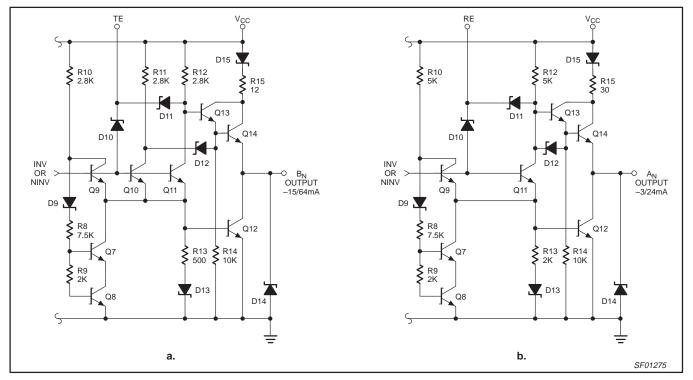

A characteristic example of the output structures found throughout the 74FXXXX Light Load product line is the 74F657 Parity Bus Transceiver, which has two basic output designs. Figure 4 illustrates the74F657's output structure designs of these output structures: A<sub>N</sub> Port's output (Figure 4b) is guaranteed to handle –3/+24mA (2.4/0.5V V<sub>OH</sub>/V<sub>OL</sub>), and the B<sub>N</sub> Port (Figure 4a) can drive greater than –15/+64mA (2.0/0.55V V<sub>OH</sub>/V<sub>OL</sub>). The A<sub>N</sub> Port is designed to drive the chip side of the PC board to backplane interface, while the B<sub>N</sub> Port is capable of driving PC board data transmission lines and backplane signal line with a characteristic impedance as low as 70Ω.

Referring back to Figure 1a, the base drive current for Q9/10/11 comes from either R6 for an inverting output or R7, if the output is non-inverting. For the inverting case, D4 is back-biased when the base voltage applied to Q1 ( $\geq$ 2.0V<sub>OH</sub>) and Q9 base drive is supplied from R6. Q9's base is clamped at the sum of base-emitter forward biased voltage drops of Q9/10/11 and Q12. Q12's base drive primarily comes from R10/11/12 when Q9/10/11 are ON.

When Q9/10/11 begin to turn-ON, the base drive for Q12 must first overcome the R13/D13 base clamp before current can flow into Q12's base. During the output voltage HIGH to LOW transition, this delay minimizes totem-pole feed-through current into the ground lead by allowing the collector of Q11 (Phase Splitter Transistor – Q<sub>PS</sub>) to pull down toward 1 V<sub>BE</sub> + 1 V<sub>CEsat</sub> and, thereby, turning-OFF the Q13/14 Darlington totem-pole output pull-up driver before Q12 completely turns-ON.

When the gate input switches from V<sub>IH</sub> to V<sub>IL</sub> ( $\leq$  0.8V), the charge stored in D2 discharges through the base-emitter of Q2. Q2 (through D3) quickly pulls the bases of Q9/10/11 toward ground. When the collector of Q9 rises high enough (~1.3V) to forward bias the Q12

base clamping network of D9/R8/R9/Q7/Q8, Q12 is quickly turned-OFF before the Q13/14 totem-pole pull-up can turn-ON. This design minimizes feed-through ground during the output voltage LOW to HIGH transition.

The 3-State, totem-pole output structures of both the  $A_N$  and  $B_N$  ports have Schottky blocking diodes, D15, in their pull-ups. Their purpose is to block leakage current form flowing into the outputs when  $V_{CC}$  is either open or shorted to ground. These diodes will not let current flow until the output voltage reaches 5.5V.

The  $I_{OS}$  limiting resistors, R15, limit the amount of current that can be sourced from the HIGH to ground. Note that R15 is  $12\Omega$  for the A<sub>N</sub> outputs. Therefore, under the same conditions, the B<sub>N</sub> output pull-up structure will be able to source 2.5 times more current than the A<sub>N</sub> outputs.

#### **Minimizing Ground Bounce**

Refer to *Application Note AN213 "74F30XXX Family Applications"* for a detailed discussion of "ground bounce" and internal noise generation due to reduced ground lead inductance. When a TTL output switches fro LOW to HIGH or HIGH to LOW, some feed-through or crossover current will be injected into the ground lead of the IC while both the pull-up and pull-down output drive structures are ON simultaneously. The larger the number of switched outputs, the larger the feed-through current and "ground bounce".

"Ground bounce" directly affects the input threshold of a gate, and therefore, its noise sensitivity. The newer output structure design used in the "Light Load" NPN input product line allow all outputs to switch simultaneously with minimal "ground bounce".

Figure 4. Two Typical "Light Load" Output Structures (74F657)

# 74FXXXX "Light Load" input products

| Part<br>Number | #<br>Bits | Polarity    | Output | Broad-<br>side | I <sub>OH</sub> /I <sub>OL</sub><br>MIN | Storage | Speed  | Parity | Comments                                                             |

|----------------|-----------|-------------|--------|----------------|-----------------------------------------|---------|--------|--------|----------------------------------------------------------------------|

| "Light Load"   | Buffers   | and Line D  | rivers |                |                                         |         |        |        |                                                                      |

| 74F125/6       | 4-bit     | NINV        | 3-St   | No             | -15/64mA                                | None    | 6.5ns  | No     | Separate output enables (F125 = $\overline{EN}$ ; F126 = $EN$ )      |

| 74F365/6       | 6-bit     | NINV        | 3-St   | No             | -15/64mA                                | None    | 7.5ns  | No     | Common output enable                                                 |

| 74F367/8       | 6-bit     | INV         | 3-St   | No             | -15/64mA                                | None    | 7.5ns  | No     | Two output enables controlling 3 outputs each                        |

| 74F455/6       | 8-bit     | INV/NINV    | 3-St   | Yes            | -15/64mA                                | None    | 7.5ns  | Yes    | Multiple/Ctr package GND pin,<br>$\Sigma_E$ , $\Sigma_O = -15/64$ mA |

| 74F540/1       | 8-bit     | INV/NINV    | 3-St   | Yes            | -15/64mA                                | None    | 7.5ns  | No     | Broadside pinout of F240                                             |

| 74655A/6A      | 8-bit     | INV/NINV    | 3-St   | Yes            | -15/64mA                                | None    | 7.5ns  | Yes    | $\Sigma_{\text{E}}, \Sigma_{\text{O}} = -15/64\text{mA}$             |

| 74F804/1804    | 6-bit     | 2I-NAND     | 3-St   | No             | -48/48mA                                | None    | 4.0ns  | No     | PNP Hex 2-Input NAND gate,<br>F1804 has center supply pins           |

| 74F805/1805    | 6-bit     | 2I-NOR      | 3-St   | No             | -48/48mA                                | None    | 4.0ns  | No     | PNP Hex 2-Input NOR gate,<br>F1805 has center supply pins            |

| 74F808/1808    | 6-bit     | 2I-AND      | 3-St   | No             | -48/48mA                                | None    | 5.0ns  | No     | PNP Hex 2-Input AND gate,<br>F1808 has center supply pins            |

| 74F827/8       | 10-bit    | NINV/INV    | 3-St   | Yes            | -15/64mA                                | None    | 9.0ns  | No     |                                                                      |

| 74F832/1832    | 6-bit     | 2I-OR       | 3-St   | No             | -48/48mA                                | None    | 5.5ns  | No     | PNP Hex 2-Input OR gate,<br>F1832 has center supply pins             |

| 74F1240/1      | 8-bit     | INV/NINV    | 3-St   | No             | -15/64mA                                | None    | 6.5ns  | No     | Light Load pin replacement for F240/1                                |

| 74F1244        | 8-bit     | INV/NINV    | 3-St   | No             | -15/64mA                                | None    | 7.0ns  | No     | Light Load pin replacement for F244                                  |

| 74F30240/4     | 8-bit     | INV/NINV    | OC     | Yes            | OC/160mA                                | None    | 15.0ns | No     | Octal, 30Ω PC board data<br>transmission line driver                 |

| "Light Load"   | Registe   | rs and Latc | hes    | •              |                                         |         |        |        |                                                                      |

| 74F166         | 8-bit     | NINV        | 3-St   | Yes            | -1/20mA                                 | S/R     | 110MHz | No     | Serial/Parallel-In, Serial-Out                                       |

| 74F195         | 4-bit     | NINV        | 3-St   | Yes            | -1/20mA                                 | S/R     | 110MHz | No     | Serial/Parallel-In, Serial-Out                                       |

| 74F273         | 8-bit     | NINV        | 3-St   | No             | -1/20mA                                 | S/R     | 120MHz | No     | D-type flip-flops                                                    |

| 74F377         | 8-bit     | NINV        | 3-St   | No             | -1/20mA                                 | S/R     | 100MHz | No     | D-type flip-flops                                                    |

| 74F595         | 8-bit     | NINV        | 3-St   | Yes            | -3/20mA                                 | S/R     | 80MHz  | No     | S or P-In, Serial-Out<br>with D-register output storage              |

| 74F597         | 8-bit     | NINV        | 3-St   | Yes            | -3/20mA                                 | S/R     | 80MHz  | No     | S or P-In, Serial-Out<br>with D-register input storage               |

| 74F598         | 8-bit     | NINV        | 3-St   | Yes            | -3/20mA                                 | S/R     | 80MHz  | No     | F597 with multiplexed inputs and outputs                             |

| 74F821/2       | 10-bit    | NINV/INV    | 3-St   | Yes            | -15/64mA                                | Reg     | 100MHz | No     | Data, Master Reset,<br>Output Enables & Clock EN inputs              |

| 74F823/4       | 9-bit     | NINV/INV    | 3-St   | Yes            | -15/64mA                                | Reg     | 100MHz | No     | Data, Master Reset,<br>Output Enables & Clock EN inputs              |

| 74F825/6       | 8-bit     | NINV/INV    | 3-St   | Yes            | -15/64mA                                | Reg     | 100MHz | No     | Data, Master Reset,<br>Output Enables & Clock EN inputs              |

| 74F841/2       | 10-bit    | NINV/INV    | 3-St   | Yes            | -15/48mA                                | Latch   | 100MHz | No     | Data, Master Reset,<br>Output Enables & LE Enable inputs             |

| 74F843/4       | 9-bit     | NINV/INV    | 3-St   | Yes            | -15/48mA                                | Latch   | 100MHz | No     | Data, Master Reset,<br>Output Enables & LE Enable inputs             |

| 74F845/6       | 8-bit     | NINV/INV    | 3-St   | Yes            | -15/48mA                                | Latch   | 100MHz | No     | Data, Master Reset,<br>Output Enables & LE Enable inputs             |

Table 1. The 74F "Light Load" Input Products

# 74FXXXX "Light Load" input products

| A | Ν | 2 | 1 | 5 |

|---|---|---|---|---|

|---|---|---|---|---|

| Part<br>Number | #<br>Bits | Polarity     | Output                | Broad-<br>side | I <sub>OH</sub> /I <sub>OL</sub><br>MIN | Storage             | Speed  | Parity | Comments                                                                                                                                                 |

|----------------|-----------|--------------|-----------------------|----------------|-----------------------------------------|---------------------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Light Load"   | Transce   | eivers/Latch | ed or Regist          | ered Trans     | sceivers                                |                     |        |        |                                                                                                                                                          |

| 74F545         | 8-bit     | NINV         | A <sub>N</sub> = 3-St | Yes            | -3/24mA                                 | None                | 7.0ns  | No     | Pin-for-pin replacement for the Intel 8286                                                                                                               |

|                |           |              | B <sub>N</sub> = 3-St | Yes            | –15/64mA                                | None                | 7.0ns  | No     |                                                                                                                                                          |

| 74F588         | 8-bit     | NINV         | $A_N = 3-St$          | Yes            | 3/24mA                                  | None                | 7.5ns  | No     |                                                                                                                                                          |

|                |           |              | B <sub>N</sub> = 3-St | Yes            | -15/64mA                                | None                | 7.5ns  | No     | IEEE-488/GPIB with output line termination resistors                                                                                                     |

| 74F620/23      | 8-bit     | INV/NINV     | B <sub>N</sub> = 3-St | Yes            | -15/64mA                                | None                | 7.5ns  | No     | $A_N \leftrightarrow B_N, A_N = -3/24mA$                                                                                                                 |

| 74F621/22      | 8-bit     | NINV/INV     | B <sub>N</sub> = OC   | Yes            | OC/64mA                                 | None                | 13.0ns | No     | $A_N \leftrightarrow B_N, A_N = OC/24mA$                                                                                                                 |

| 74F640         | 8-bit     | INV          | A/B = 3-St            | Yes            | -15/64mA                                | None                | 7.5ns  | No     | $A_N \leftrightarrow B_N$                                                                                                                                |

| 74F641/42      | 8-bit     | NINV/INV     | A/B = OC              | Yes            | OC/64mA                                 | None                | 13.0ns | No     | $A_N \leftrightarrow B_N$                                                                                                                                |

| 74F646/48      | 8-bit     | NINV/INV     | A/B = 3-St            | Yes            | -15/64mA                                | 2-Reg               | 11.5ns | No     | $\begin{array}{l} A_N \leftrightarrow B_N,  \text{Registers for } A_N \And B_N \\ \text{ports, 80MHz (Min.)} \end{array}$                                |

| 74F647/49      | 8-bit     | NINV/INV     | A/B = OC              | Yes            | OC/64mA                                 | 2-Reg               | 19.5ns | No     | $\begin{array}{l} A_N \leftrightarrow B_N,  \text{Registers for } A_N \And B_N \\ \text{ports, 40MHz}  (\text{Min.}) \end{array}$                        |

| 74F651/2       | 8-bit     | INV/NINV     | A/B = 3-St            | Yes            | -15/64mA                                | 2-Reg               | 12.5ns | No     | $\begin{array}{l} A_{N} \leftrightarrow B_{N},  Registers  for  A_{N} \And B_{N} \\ ports,  80MHz  (Min.) \end{array}$                                   |

| 74F653         | 8-bit     | NINV/INV     | B <sub>N</sub> = 3-St | Yes            | -15/64mA                                | B <sub>N</sub> -Reg | 11.0ns | No     | $A_N \rightarrow B_N$ , $B_N$ port = 85MHz (Min.)                                                                                                        |

|                |           |              | A <sub>N</sub> = OC   | Yes            | OC/64mA                                 | A <sub>N</sub> -Reg | 20.0ns | No     | $B_N \rightarrow A_N$ , $A_N$ port = 45MHz (Min.)                                                                                                        |

| 74F657         | 8-bit     | NINV         | B <sub>N</sub> = 3-St | Yes            | -15/64mA                                | None                | 8.0ns  | Yes    | $\begin{array}{l} A_N \leftrightarrow B_N,  \text{Parity I/O},  \text{Odd/}\overline{Even}   \text{In} \\ \&  \overline{Error}   \text{Out} \end{array}$ |

| 74F861/2       | 10-bit    | NINV/INV     | A/B = 3-St            | Yes            | -15/64mA                                | None                | 10.0ns | No     | $A_N \leftrightarrow B_N$                                                                                                                                |

| 74F863/4       | 9-bit     | NINV/INV     | A/B = 3-St            | Yes            | -15/64mA                                | None                | 10.0ns | No     | $A_N \leftrightarrow B_N$                                                                                                                                |

| 74F1242/3      | 8-bit     | INV          | A/B = 3-St            | No             | -15/64mA                                | None                | 7.5ns  | No     | $A_N \leftrightarrow B_N$ , Light Load pin replacements for F240/1                                                                                       |

| 74F1245        | 8-bit     | INV          | A/B = 3-St            | Yes            | -15/64mA                                | None                | 6.5ns  | No     | $A_N \leftrightarrow B_N$ , Light Load pin replacements for F245                                                                                         |

| 74F30245       | 8-bit     | NINV         | B <sub>N</sub> = OC   | Yes            | OC/160mA                                | None                | 15.0ns | No     | Octal, $30\Omega$ transmission line driver, $B_N = 0.6mA I_{IL}$                                                                                         |

|                |           |              | A <sub>N</sub> = 3-St | Yes            | -3/24mA                                 | None                | 7.0ns  | No     | A <sub>N</sub> "Light Load" inputs                                                                                                                       |

| 74F30640       | 8-bit     | INV          | B <sub>N</sub> = OC   | Yes            | OC/160mA                                | None                | 15.0ns | No     | Octal, 30 $\Omega$ transmission line driver, $B_N = 0.6 \text{mA I}_{\text{IL}}$                                                                         |

|                |           |              | A <sub>N</sub> = 3-St | Yes            | -3/24mA                                 | None                | 7.0ns  | No     | A <sub>N</sub> "Light Load" inputs                                                                                                                       |

| "Light Load"   | Transce   | eivers/Latch | ed or Regist          | ered Trans     | sceivers                                |                     |        | •      |                                                                                                                                                          |

| 74F85          | 4-bit     | INV/NINV     | 3-St                  | No             | -1/20mA                                 | None                | 14.5ns | No     | 4-bit magnitude comparator                                                                                                                               |

| 74F280B        | 9-bit     | NINV         | 3-St                  | Yes            | -1/20mA                                 | None                | 14.5ns | Yes    | Parity generator/checker                                                                                                                                 |

| 74F604         | 16-bit    | NINV         | 3-St/OC               | Yes            | 3/24mA                                  | D-Reg               | 80MHz  | No     | Dual 8-bit registered octal multiplexer                                                                                                                  |

### NOTES:

All parameters are worst-case, unless otherwise specified. 3-St = 3-State

OC = Open Collector Reg = LOW-to-HIGH edge clocked D-type register

Latch = HIGH logic level on the latch enable logic data passes directly through D-type latch = HIGH-to-LOW logic level transition of the latch enable, data is stored in the D-type latch S/R = Shift Register

### 74FXXXX "Light Load" input products

### AN215

#### Data sheet status

| Data sheet<br>status      | Product<br>status | Definition <sup>[1]</sup>                                                                                                                                                                                                                                       |

|---------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development       | This data sheet contains the design target or goal specifications for product development.<br>Specification may change in any manner without notice.                                                                                                            |

| Preliminary specification | Qualification     | This data sheet contains preliminary data, and supplementary data will be published at a later date.<br>Philips Semiconductors reserves the right to make chages at any time without notice in order to<br>improve design and supply the best possible product. |

| Product specification     | Production        | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                            |

[1] Please consult the most recently issued datasheet before initiating or completing a design.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition - Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information - Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

**Philips Semiconductors** 811 East Argues Avenue P.O. Box 3409 Sunnyvale, California 94088-3409 Telephone 800-234-7381

© Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

Date of release: 05-96

Document order number:

9397 750-05223

Let's make things better.